研究背景

基于超细晶硅纳米沟道的围栅晶体管(GAA-FETs)因其卓越的静电控制能力,已成为3 nm以下工艺节点的主流器件架构。然而,为实现更高集成密度的单片三维集成架构,需要在缺少单晶硅衬底的堆叠层中,仅依赖全低温工艺(<450 oC)直接制备超细晶硅沟道和高性能GAA-FET器件——这也成为突破高性能三维集成硅基逻辑/存储的核心障碍之一。因此,针对传统微缩刻蚀(Etching)制备工艺所面临的技术挑战,探索一条与之互补的催化生长(Growth)集成制备新策略具有重要的意义。

High-performance gate-all-around field effect transistors based on orderly arrays of catalytic Si nanowire channels

Wei Liao, Wentao Qian, Junyang An, Lei Liang, Zhiyan Hu, Junzhuan Wang, Linwei Yu*

Nano-Micro Letters (2025)17: 154

https://doi.org/10.1007/s40820-025-01674-8

本文亮点

1. 高密度硅纳米线(SiNW)阵列生长集成:基于面内固-液-固(IPSLS)机制,在绝缘衬底上直接生长出直径仅22.4 ± 2.4 nm、线间距90 nm的超细SiNWs,展现出极高的均匀性和精确性。

2. 创新的悬空接触策略:开发了一种独特悬空技术,成功固定并释放超细 SiNWs 作为准一维通道,悬空长度可超 500 nm,为全栅结构提供了理想条件。

3. 高性能GAA-FETs突破:首次基于催化SiNWs沟道实现高性能GAA-FETs,开关比达10⁷,亚阈值摆幅低至66 mV/dec,接近理论极限。

内容简介

本文聚焦于通过面内固-液-固(IPSLS)技术制备有序超细SiNWs阵列,并首次将其应用于高性能GAA-FET。南京大学余林蔚等人利用预设计的高密度引导台阶,在绝缘衬底上直接生长有序排列的超细硅纳米线阵列。这些纳米线具有直径均匀(DNW = 22.4 ± 2.4 nm)和紧密间距(90 nm)的特点,非常适合用于构建高性能GAA-FET器件。随后,开发了一种特殊的悬空接触策略,成功固定并释放了这些超细硅纳米线作为准一维沟道材料。结合优化的源/漏(S/D)金属接触(Pt/Au),成功制备出高性能GAA-FET,其开关比(Ion/Ioff)达到10⁷,亚阈值摆幅(SS)仅为66 mV/dec,接近理论极限值(60 mV/dec)。这一性能媲美于采用电子束光刻(EBL)和极紫外光刻(EUV)的先进GAA-FETs,突破了催化生长纳米线器件的性能瓶颈。

图文导读

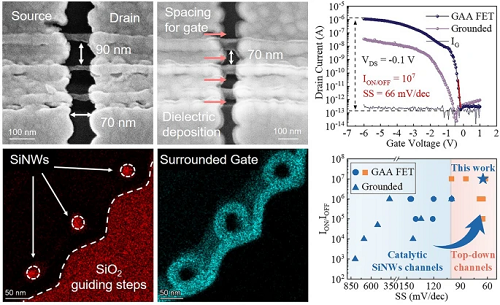

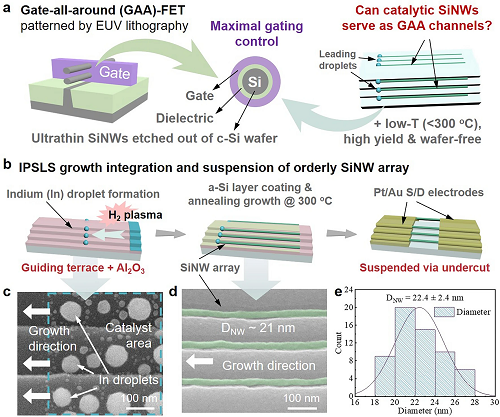

I 硅纳米线生长与悬空技术

图1a对比了传统EUV光刻和催化生长方式制备的GAA-FET结构。图1b详细描述了IPSLS纳米线生长及悬空释放过程:首先通过光刻和循环交替刻蚀形成密排引导台阶,随后沉积40 nm Al₂O₃牺牲层;然后沉积4 nm铟(In)催化剂条带,在PECVD中用氢等离子处理形成直径70 ± 11 nm的铟液滴(图1c);最后垫积7 nm非晶硅并在真空中退火,使液滴沿台阶吸收非晶硅并生长硅纳米线。图1d的扫描电镜(SEM)图像显示,生长出的硅纳米线均匀分布于台阶根部,直径约21 nm。图1e对其他区域生长的纳米线直径进行了统计,进一步确认纳米线直径为 22.4 ± 2.4 nm,具有高均匀性,适合用于构建高性能GAA-FET器件。

图1. a) 通过EUV光刻及催化生长集成的GAA结构示意图。b) IPSLS纳米线生长及悬空示意图。c) 催化剂区域和d) SiNWs的典型SEM图像。e) 不同区域IPSLS SiNWs的直径统计。

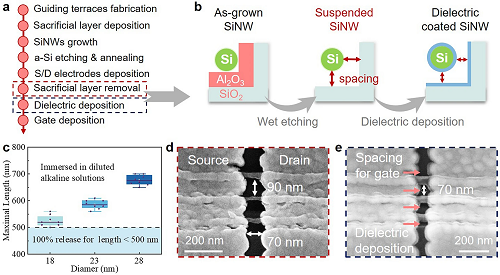

II GAA-FET 制备流程

图2a列举了GAA-FET的完整制造流程程,突出显示了沟道悬空释放和介电层沉积两个关键步骤(虚线框)。图2b示意了通过稀释碱溶液(2.5%)蚀刻 Al₂O₃牺牲层释放纳米线沟道的过程。图2c中统计表明,纳米线最大悬空长度与其直径相关。例如,直径28 nm的纳米线悬空长度可达 700 nm,即使对于直径18 nm的纳米线,其悬空长度也大于500 nm。图2d-e展示了悬空纳米线及其沉积介质层后的SEM图像。

图2. a) SiNW GAA-FETs的制造流程。b) 湿法释放和介电层沉积步骤的示意图。c) 不同直径SiNW沟道的悬空长度统计。d-e) 悬空SiNWs及沉积3 nm Al₂O₃和7 nm HfO₂后的SEM图像。

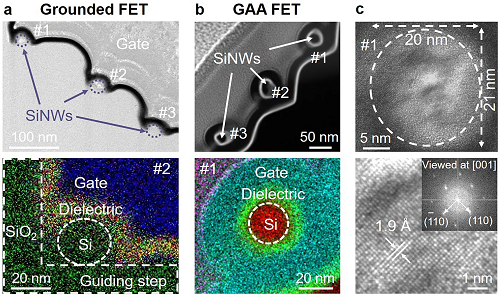

III 器件结构表征

图3a-b分别展示了普通器件和GAA器件的横截面高分辨透射电镜(HR-TEM)图像。普通器件中(图3a),纳米线沟道仅能顶部受栅极调控,而GAA 器件可实现栅极的全方向包裹(图3b),能提供最大电容耦合。图3c中局部放大的HR-TEM图像揭示,硅纳米线截面呈椭圆形(高为20 nm,宽为21 nm),为单晶结构。其中,晶格间距为0.19 nm晶格条纹对应Si (110)面,快速傅里叶变换(FFT)图像显示该纳米线生长方向为Si <100>晶向。

图3. IPSLS SiNW-FETs 的横截面 TEM 图像及相应的高分辨EDS图谱:a) 普通 FET和b) GAA FET。c) GAA FET中#1号SiNW的局部放大HR-TEM 图像及相应电子衍射图案。

IV 器件电学性能

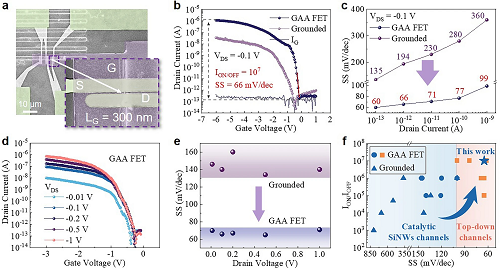

图4a为GAA-FET的SEM图像,其沟道长度为300 nm,S/D电极为Pt/Au电极(12/55 nm)。图4b中的转移特性曲线表明,在VDS = -0.1 V时,GAA-FET 的开关比可达10⁷,SS为66 mV/dec,漏电流低于0.1 pA;相比之下,普通FET 的SS为150 mV/dec。图4c和图4e系统比较了两种器件在不同源/漏电流以及电压下的SS,GAA-FET在各种情况下均展现了更好的性能。图4f对比了文献中催化纳米线与自上而下工艺制备的SiNW-FETs的SS和开关比。可以看到,本研究中的GAA-FET性能远超催化生长的纳米线器件,媲美采用电子束光刻(EBL)和极紫外光刻(EUV)的先进GAA-FETs。

图4. a) GAA-FET的SEM图像。普通FET和GAA-FET:b) 转移曲线,c) SS−IDS 曲线,e) SS−VDS曲线。d) GAA-FET的转移曲线。f) 器件性能对比:基于文献中催化SiNW和自上而下蚀刻SiNW/NS沟道的FET。

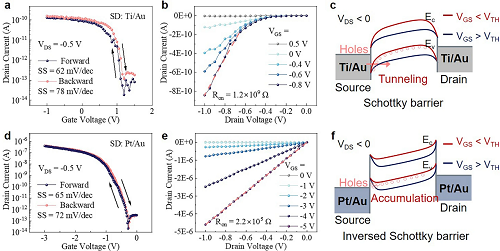

V 源/漏接触优化

图5a-d比较了Ti/Au和Pt/Au接触下的GAA-FET转移特性。其中,Ti/Au 接触开关比仅为10³,尽管SS仅为62 mV/dec;而Pt/Au接触器件开关比提高了近四个量级,达10⁷,SS为65 mV/dec。图5b-e的输出特性显示,Pt/Au接触更接近欧姆特性,开态电阻(2.2×10⁵ Ω)远低于Ti/Au(1.2×10⁹ Ω)。图 5c-f的能带图解释了这一差异:Ti(功函数4.3 eV)接触存在较大的肖特基势垒,从而限制了器件电流;而Pt(5.6 eV)形成反向肖特基势垒,有利于提升驱动电流。

图5. Ti/Au接触GAA-FET的电学性能:a) 迟滞曲线,b) 输出曲线,c) 不同栅偏压条件下的能带图。Pt/Au接触GAA FET的电学性能:d)迟滞曲线,e) 输出曲线,f) 不同栅极偏压条件下的能带图。

VI 总结

本文通过 IPSLS 技术制备了直径 22.4 ± 2.4 nm、线间距 90 nm 的有序硅纳米线阵列,并首次将其用于高性能 GAA-FETs。通过创新的悬空接触策略和优化的源/漏接触,使器件实现了10⁷的开关比和66 mV/dec的亚阈值摆幅,性能媲美自上而下EBL和EUV光刻制备的先进GAA-FETs。相比传统工艺,这种催化生长硅纳米线GAA-FET具有更高的灵活性和兼容性,能够更好地融入现有制造流程。同时,由于该技术无需依赖预先存在的单晶硅晶圆,且可在低温条件下完成,因此特别适合于堆叠式3D集成电路的设计与制造。随着该技术的进一步优化和成熟,有望推动高性能、低功耗和高集成度电子器件的快速发展,并在人工智能、感存算一体芯片等需要多层堆叠的先进领域实现广泛应用。

作者简介

关于我们

Nano-Micro Letters《纳微快报(英文)》是上海交通大学主办、在Springer Nature开放获取(open-access)出版的学术期刊,主要报道纳米/微米尺度相关的高水平文章(research article, review, communication, perspective, highlight, etc),包括微纳米材料与结构的合成表征与性能及其在能源、催化、环境、传感、电磁波吸收与屏蔽、生物医学等领域的应用研究。已被SCI、EI、PubMed、SCOPUS等数据库收录,2023 JCR IF=31.6,学科排名Q1区前3%,中国科学院期刊分区1区Top期刊。多次荣获“中国最具国际影响力学术期刊”、“中国高校杰出科技期刊”、“上海市精品科技期刊”等荣誉,2021年荣获“中国出版政府奖期刊奖提名奖”。欢迎关注和投稿。

Web: https://springer.com/40820

E-mail: editor@nmlett.org

Tel: 021-34207624

如果文章对您有帮助,可以与别人分享!:Nano-Micro Letters » 南京大学余林蔚等:超细硅纳米线阵列的生长集成并首次应用于高性能围栅晶体管

Nano-Micro Letters

Nano-Micro Letters

韩国科研院Jinwoo Lee等:为高性能纤维状储能器件设计氧化还原聚合物电解质

韩国科研院Jinwoo Lee等:为高性能纤维状储能器件设计氧化还原聚合物电解质 中科院兰州化物所毕迎普等:高活性BiVO₄光阳极耦合高选择性Co-N₅阴极实现高效CO₂还原

中科院兰州化物所毕迎普等:高活性BiVO₄光阳极耦合高选择性Co-N₅阴极实现高效CO₂还原 仿生离子传感器综述:将自然机制转化为传感技术

仿生离子传感器综述:将自然机制转化为传感技术 武大侯佑民、陈重学&华科王康丽等:吸附调控界面稳定性实现高度稳定且安全的 4.6 V 钴酸锂正极

武大侯佑民、陈重学&华科王康丽等:吸附调控界面稳定性实现高度稳定且安全的 4.6 V 钴酸锂正极