研究背景

新兴的二维(2D)半导体因其固有的原子级厚度而成为超大规模晶体管最有前途的材料之一。随着堆叠工艺的发展,纳米片场效应晶体管(NSFET)和互补场效应晶体管(CFET)的复杂性和成本不断上升。根据国际器件与系统路线图(IRDS),1 nm技术节点将基于Si-CFET工艺,但尚未得到公开证实,这表明仍存在更多可能性。二维半导体的微型化优势促使我们探索其降低工艺成本的潜力,同时在面积、功耗和速度方面与下一代节点的性能相匹配。

A valuable and low-budget process scheme of equivalized 1 nm technology node based on 2D materials

Yang Shen, Zhujun Yao, Zhejia Zhang, Mengge Jin, Jintian Gao, Yuhan Zhao, Wenzhong Bao*, Yabin Sun*, He Tian*

Nano-Micro Letters (2025)17: 191

https://doi.org/10.1007/s40820-025-01702-7

本文亮点

1. 二维半导体纳米片场效应晶体管(NSFET)的制备:本文制备了一组基于二维半导体纳米片的场效应晶体管,即2D-NSFET,其中沟道由两层堆叠的二维半导体纳米片组成,并由三个栅极同时控制两个并行沟道。

2. 验证2D-NSFET在1 nm节点的替代潜力:构建了完整的工艺框架,验证了使用2D-NSFET替代1 nm节点硅基互补场效应晶体管(CFET)的可行性,提出了一种基于二维材料的1 nm技术节点解决方案,即“2D等效1 nm”节点。

3. 在固定功耗下实现频率提升:水平微缩的2D-NSFET在固定功耗下将频率提升28%,并在16位RISC-V CPU中表现出类似的性能增长趋势。

内容简介

华东师大孙亚宾&清华大学田禾&复旦大学包文中等建立了一个完整的工艺框架,设计并制造了一组基于二维材料的纳米片场效应晶体管(NSFET),用于提取关键参数和评估性能。为了进行基准测试,研究将2D-NSFET的尺寸缩放至与硅基CFET在平均器件单元面积上相同。在此条件下,2D-NSFET在固定功耗下的频率提升了36%,验证了其在1 nm节点替代Si-CFET的可行性,并提出了一种基于二维材料的1 nm技术解决方案,即“2D等效1 nm”节点。得益于二维半导体材料更小的特征长度,微缩后的2D-NSFET在固定功耗下实现了28%的频率提升。此外,通过开发标准单元库,这些器件在16位RISC-V CPU中展现出类似的性能增长趋势。本研究量化并突出展示了二维半导体在先进节点上的优势,为其在高速、低功耗集成电路中的应用提供了新的可能性。

图文导读

I 二维纳米片场效应晶体管(2D-NSFET)的制备与表征

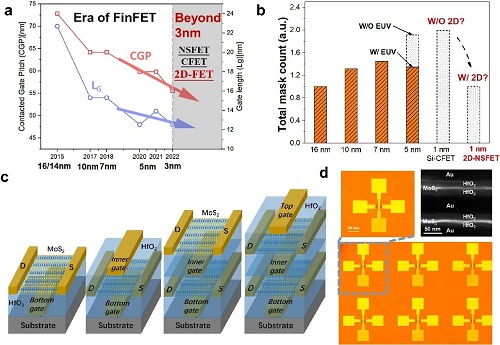

由于CFET在功耗、性能和面积(PPA)方面的显著优势,它已迅速成为克服半导体器件微型化方面即将出现的限制的有力候选器件,并有望应用于3纳米技术节点以外的领域(图1a)。随着尺寸的不断缩小,难以彻底解决的潜在物理限制促使研究人员继续探索其他选择。

在这种情况下,在1纳米节点采用二维半导体将大幅减少光掩膜总数,就像在5纳米节点采用EUV技术一样,这有利于降低工艺复杂性和成本(图1b)。值得注意的是,这里的所有技术节点都以硅基集成电路(IC)为参照。为了验证这一想法,我们首先准备了一组MoS₂ NSFET,用于校准我们的基础物理模型。图 1c显示了本研究制备的2D-NSFET的典型工艺和结构示意图。沟道材料是通过化学气相沉积(CVD)技术生长的高质量三层MoS₂薄膜,其中两个平行的MoS₂沟道由三个栅极同时控制。这种设计实现了具有高迁移率和低亚阈值摆动的高性能 MoS₂ NSFET,证明了这种结构在提高器件性能方面的潜力。本研究提出的MoS₂ NSFET有望实现晶圆级大规模集成。图1d显示了MoS₂ NSFET和器件阵列的光学显微镜图像,证实了该工艺的高度均匀性和可扩展性。

图1. (a) 从16纳米到3纳米以上节点的栅极长度和CGP演进;(b) 从16纳米到5纳米节点的总掩膜数演进,其中5纳米节点的EUV的出现实现了掩膜数的减少,预计在1纳米节点,使用2D-NSFET可实现光掩膜数比1纳米节点的Si-CFET减少一半;(c) MoS₂ NSFET工艺流程图,包含两层导电沟道;(d) MoS₂ NSFET器件和阵列的光学照片,以及典型MoS₂ NSFET的STEM截面图,显示二维沟道、栅极电介质和栅极金属的分布。

II 二维纳米片场效应晶体管(2D-NSFET)与硅基晶体管在1 nm节点下的性能对比与校准

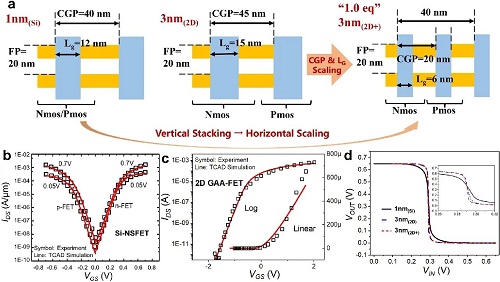

图2a显示了一种方案,CGP和LG分别减小到20 nm和6 nm,从而将平面尺寸上的单位器件面积减半(称为3 nm(2D+),或“2D eq 1 nm”)。对于3 nm和1 nm节点的Si-NSFET仿真,在此尺度下的仿真包括许多复杂的物理模型。模拟的电气特性与2017年报告的12 nm LG NSFET实验数据进行了校准(图2b)。通过设置相同的结构尺寸和校准物理参数,最终的实验数据和仿真结果可以很好地吻合,这验证了上述建模设置的合理性。为了更准确地模拟二维场效应晶体管的性能,我们建立了一个跨尺度模拟框架,通过密度泛函理论(DFT)计算材料的基本参数,然后将其引入器件模拟中进行预测。为了将MoS₂ NSFET校准到上述制备的器件,使用了扩展数据图6中给出的DFT计算参数,并如图2c所示拟合了IDS-VGS曲线。图2d显示了MoS₂ NSFET器件在高分辨率透射电子显微镜(STEM)下的横截面,从中可以清楚地看到双层平行MoS₂沟道、作为栅极电介质的HfO₂以及栅极金属电极的堆叠结构。

图 2. (a) 1 nm(Si)、3 nm(2D)和 3 nm(2D+)节点的平均器件布局比较;(b) 模拟传输特性与实验Si-NSFET(LG=12 nm)传输特性的校准;(c) 2D NSFET传输特性的校准;(d) 基于三种不同器件的逆变器的电压传输特性(VTC)。

III 3 nm(2D+)节点、3 nm(2D)节点和 1 nm(Si)节点,Si-NSFET和WS₂-NSFET 的 CGP 固定为45 nm,LG从18 nm缩小到6 nm时器件电气特性的比较

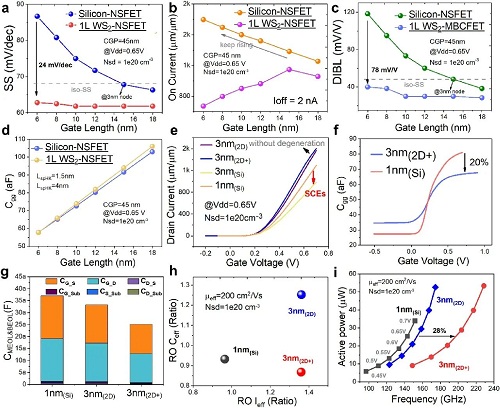

将LG从18 nm缩短到6 nm,以观察Si-NSFET和2D-NSFET的性能变化。图3a-d显示了改变LG时SS、DIBL、ION和栅极电容Cgg的变化。模拟了3 nm(2D+)、1 nm(Si)、基于NSFET的 3 nm(Si)、3 nm(2D)等节点的器件电气特性(图3e)。由2D-NSFET小型化形成的3 nm(2D+)节点的IDS几乎没有衰减。相比之下,硅基器件的IDS从3 nm节点到1 nm节点时略有增加,这相当于LG从15 nm缩短到12 nm。当ION下降、VGS=VDD时的电流升高时,意味着IOFF升高,器件ION/IOFF降低,从而导致功耗增加。这反映了硅基器件的短沟道效应。模拟了1 nm(硅)和3 nm(2D+)节点器件的C-V特性,结果如图3f所示。与1 nm(硅)相比,3 nm(2D+)节点器件的栅极电容降低了约20%,这是因为LG减小到只有6 nm。为了展示器件内部各部分寄生电容的变化,图3g显示了器件四个端口(包括 CG_S、CG_D、CD_S、CG_sub、CD_sub 和 CS_sub)之间的CMEOL&BEOL电容。CG_S和CG_D是Cgg的主要部分,它们随着LG的减小而减小,这与图3f中的结果相符。

上述结果表明,3纳米(2D+)在功耗和速度方面都比1纳米(硅)具有理论优势。为了在电路层面量化这一优势,构建了一个15级环形振荡器(RO)电路,每个逆变器级都有三个扇出。图3h显示了上述三种器件在固定电压VDD为0.65V时提取的等效电容和等效电流。与之前提取的ION和栅极电容的趋势类似,3nm(2D+)节点的等效电容最小,等效电流最大。随着RO的电源电压从0.45V逐渐升高到0.7V,通过电路仿真提取了不同节点器件的有功功率与频率之间的关系,如图3i所示。

图 3. 在3 nm(2D+)节点、3 nm(2D)节点和1 nm(Si)节点,Si-NSFET和WS2-NSFET的CGP固定为45nm,LG从18 nm缩小到6 nm时器件电气特性的比较。(a) SS变化,当LG小于12 nm时,Si-NSFET的SS会急剧下降;(b) ION变化,由于二维材料的特征长度较小,即使LG缩至6 nm,WS2-NSFET的ION也会继续增加,而当LG缩至6 nm时,Si-NSFET的ION会持续下降;(c) DIBL变化,其趋势与SS相似;(d) Cgg变化,EOT和栅极尺寸是Cgg的主要影响因素;(e) 与3 nm(2D)、3 nm(2D+)、3 nm(Si)和1 nm(Si)四种器件相对应的线性传输特性;(f) 3 nm(2D+) 和 1 nm(Si) 对应器件的Cgg-VGS关系,由于LG缩短,3 nm(2D+)器件的Cgg-VGS降低了20%;(g) CMEOL&BEOL与线路中端(MEOL)和线路后端(BEOL)寄生电容的比较;(h) 从RO电路中提取的等效电容和等效电流的比较;(i) RO电路的功率频率比较。

IV 基于二维材料和硅的16位RISC-V CPU系统级电路的性能比较

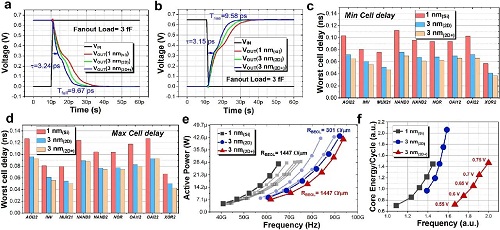

图4显示了不同节点的硅基电路和二维电路的系统级评估,比较了这些器件在开源16位RISC-V CPU中的功耗和延迟性能。合成源寄存器传输级(RTL)代码后,整个CPU由9个组合逻辑门组成,包括AOI22、INV、MUX21、NAND3、NAND2、NOR、OAI12、OAI22和XOR2。作为反相器的典型代表,我们进行了门级瞬态仿真。3 nm(2D+)节点的传播延迟和下降延迟最小,分别为3.24 ps和9.67 ps,负载电容为3 fF(图4a)。图4b中显示的输出上升沿也反映了同样的趋势,1 纳米(硅)逆变器的动态延迟最差。

经过标准单元表征后,9个逻辑门在不同的输入条件下产生了不同的单元延迟。图4c和图4d分别显示了最小单元延迟和最大单元延迟的变化趋势。当工作电压设置为0.65 V时,结果显示与1 nm(硅)节点相比,3 nm(2D)和3 nm(2D+)的所有栅极延迟都明显减少。这可以归因于2D器件可以在如此小的 LG尺寸下保持较高的ION/IOFF。

在相同的电源电压下,“2D eq 1 nm”(即 3 nm(2D+))仍然比 1 nm(Si)功耗更低,速度更快(图4e)。这表明,考虑到RBEOL和CBEOL的 “2D eq 1 nm ”可以替代传统解决方案,在器件达到目标总体指标的情况下实现成本降低和效率提高。与3 nm(2D)相比,“2D eq 1 nm ”在固定频率下可降低17%的功率,在固定功率下可提高4%的频率。图4e还比较了不同节点方案在不同RBEOL条件下的PPA变化。随着RBEOL的降低,RO的工作频率也相应提高。

图4f显示了基于二维的16位RISC-V CPU电路的PPA仿真结果。这种系统级CPU电路结合了各种组合逻辑的多样性,更符合最终芯片上的结果。在仿真中,电源电压以0.1 V为单位从0.8 V逐步升高到1.2 V。其趋势与15级环形振荡器提取的结果类似,在固定功率下,比3 nm(2D+)提高了 30%,比1 nm(Si)提高了48%。

图4. 基于二维材料和硅的16位RISC-V CPU系统级电路的性能比较。(a)和(b) 基于三种器件的逆变器仿真,包括上升沿和下降沿,从中可以提取传播延迟和下降延迟;(c)和(d) VDS=0.65V时9个不同逻辑门对应的最小和最大单元延迟。这一结果凸显了二维器件在速度方面的潜力;(e) 包括RBEOL和CBEO在内的RO电路的有功功率与频率的关系;(f) 从综合门级网表中提取的16位RISC-V CPU的功率与频率的关系,其趋势与RO电路仿真类似。

V 总结

本文重点是先进节点上二维 NSFET 的性能评估,并对RO和CPU系统等二维电路的PPA进行评估。二维半导体具有出色的横向尺寸最小化能力,在先进节点上具有突出的性能优势。这项工作提出用2D-NSFET工艺取代1纳米节点的下一代硅基CFET工艺。跨尺度仿真和系统级电路仿真验证了其可行性。未来,还可以通过构建短沟道2D-NSFET进行实验验证,从而更准确地校准仿真参数,使预测结果更具说服力。通过实验同时实现二维晶体管所需的迁移率、接触和尺寸水平是一项非常重要的挑战。然而,2D-NSFET 在先进节点上的理论优势仍使其成为下一代半导体的重要候选材料。

作者简介

关于我们

Nano-Micro Letters《纳微快报(英文)》是上海交通大学主办、在Springer Nature开放获取(open-access)出版的学术期刊,主要报道纳米/微米尺度相关的高水平文章(research article, review, communication, perspective, highlight, etc),包括微纳米材料与结构的合成表征与性能及其在能源、催化、环境、传感、电磁波吸收与屏蔽、生物医学等领域的应用研究。已被SCI、EI、PubMed、SCOPUS等数据库收录,2023 JCR IF=31.6,学科排名Q1区前3%,中国科学院期刊分区1区TOP期刊。多次荣获“中国最具国际影响力学术期刊”、“中国高校杰出科技期刊”、“上海市精品科技期刊”等荣誉,2021年荣获“中国出版政府奖期刊奖提名奖”。欢迎关注和投稿。

Web: https://springer.com/40820

E-mail: editor@nmlett.org

Tel: 021-34207624

如果文章对您有帮助,可以与别人分享!:Nano-Micro Letters » 华师大孙亚宾&清华田禾&复旦包文中等:基于二维材料的低成本等效1 nm技术节点工艺方案

Nano-Micro Letters

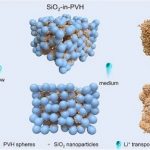

Nano-Micro Letters 东南大学孙正明、潘龙等:主客体反转策略构筑超离子导体复合固态电解质用于高倍率固态碱金属电池

东南大学孙正明、潘龙等:主客体反转策略构筑超离子导体复合固态电解质用于高倍率固态碱金属电池 韩国化学技术研究院Tae-Ho Kim等:亲水性图案化钛基多孔传输层提升高效集成式再生燃料电池能效

韩国化学技术研究院Tae-Ho Kim等:亲水性图案化钛基多孔传输层提升高效集成式再生燃料电池能效 中科大董振超&厦大黄文财等:多孔微反应器芯片常压下光催化海水分解超300小时

中科大董振超&厦大黄文财等:多孔微反应器芯片常压下光催化海水分解超300小时 清华李远等:自组装蛋白单分子层表面的二维类冰片状结构

清华李远等:自组装蛋白单分子层表面的二维类冰片状结构